这篇文章凝结了Michael Steffes的心血和汗水,他将长期积累的丰富的运算放大器知识和经验慷慨地公之于众,为行内人士提供了无私的帮助。这个系列博客文章技术性强、信息量大,绝对是适合各级设计人员的精彩教程。我从事电路设计长达40年,以前我会经常从EDN和EETimes出版的杂志上剪贴有用的资料,为我的设计之路储备知识,而我当年孜孜以求的正是这样的文章。希望你也能喜欢这篇充满经验和智慧的文章,它将帮助你强化知识,在工作中激发你的想象力和创造力。

几年前,EDN上发布了一篇出色的博客文章,探讨低速电压反馈放大器(VFA)的一些常见问题和疑问。这些问题先是在TI E2E论坛上讨论,有些问题也适用于高速运算放大器,因此就被提交到了“TI高速E2E论坛”。虽然一些高速运放的问题已经得到解决,但本文旨在对高速运算放大器所带来的独特问题进行更深入广泛的讨论。

我的同事Bruce Trump在慢速VFA型运算放大器方面的工作非常出色,他曾简明扼要地探讨了许多相关的问题。在高速方面,电压反馈放大器(VFA)、电流反馈放大器(CFA)和全差分放大器(FDA)则各有各的一系列问题。一般来说,大多数供应商将大于50MHz带宽的器件划归为高速产品。这篇文章依据Bruce关于VFA设计的原始博客,但在最相关的话题方面增加了一些对CFA和FDA的独到思考。该系列的首篇文章探讨了I/O范围问题,并且包含了对整个行业都行之有效的参数表。为了获得部分重叠,这些表中所给VFA带宽低至20MHz。

你可能会问:Michael Steffes到底是谁?在IBM和StorageTek从事了八年的模拟IC设计之后,我结束了我的高速模拟IC设计生涯,(略微)促成了首批集成式CFA运算放大器之一CLC400(基本上是一款混合CLC231的IC型号)的设计。从那以后的30年里,我陆续为5个供应商工作,横跨产品应用、销售和业务管理部门,但始终专注于高速放大器的开发、推出和design-in工具。在此期间,我参与了70多款高速放大器的产品发布,发表了一百多篇应用笔记和投稿文章。我的产品开发工作始终围绕器件定义、规范行项目和限值、特性曲线、应用文本、宏建模和design-in支持等方面。和Bruce一样,我也有幸与一些顶级模拟IC设计师密切合作,我们之间基本可以无拘无束地讨论任何放大器问题。最好的问题都来自客户——有时我们不得不请那些坐在隔壁的IC设计人员过来帮忙。

Bruce Trump的“The Signal”博客每周发布一次,内容仅涵盖VFA器件。而我这篇月刊博客自然就长一些,涵盖现代放大器产品中的3种高速器件。

在IC设计中,输出摆动范围问题是与输入摆动设计要求分开的。这里假定器件工作最好不要超过摆动范围。对所有速度范围和拓扑结构来说,输出的摆动范围通常与电源对称。如果是轨到轨输出(RRO),那么它对两个电源都是轨到轨。如果不是RRO,那它对两个电源都不是RRO。而且,如果输出不是RRO,那么输入范围通常不是轨到轨输入(非RRI),只有少数情况例外。另外,运算放大器没有地引脚,因此只要器件上的总电源电压(Vs)在指定的工作范围内,就可以对两个电源引脚上的电压进行任意组合。所得的输出摆动相对于电源总会有一个“净空(headroom)”,从而保证运算放大器能够“线性”工作。轨到轨输出级可尽可能减小这个净空。但是,为使运算放大器正常工作,仍然需要提供10mV至200mV的净空。非RRO输出需要高得多的净空,但在输出线性度对静态功耗方面往往更具优势。

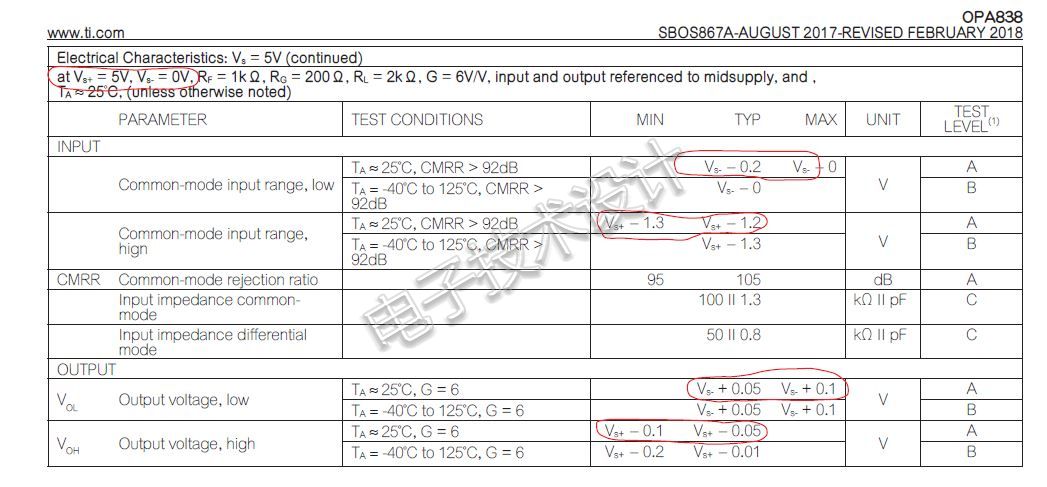

以前对运算放大器输出摆动的通俗解释是“某些指定供电电压下的±Vout”。这样表达有点啰嗦,而在最近发布的一些产品规范(如图1所示的OPA838规范)中出现了更好的表达方式,即“电源净空”。该净空规格在任意的电源电压组合下都保持不变。

图1:负轨输入(NRI)、RRO OPA838的I/O净空规格。

同时,一种较新且非常有用的输出摆动范围与输出电流关系图已成为标准的RRO特性曲线。随着拉/灌输出电流不断变大,净空要求相应增加,而“爪形”曲线这种典型方法可以为其提供更多的相关信息,甚至最新的TINA宏模型中包含了它。图2所示的这种爪形曲线来自38MHz、RRIO OPA350数据手册。图中左边的刻度是以正负电源电压(V+和V-)为参考的输出摆动范围。曲线顶部和底部最大值的变化就是与拉电流或灌电流对应的净空。

图2:RRIO OPA350的爪形曲线。

实际上,爪形曲线也是估算另一项非常重要的运算放大器输出参数,即线性输出电流的一种方法。利用爪形曲线,这一难度较大的参数可以很容易地从不同供应商数十年的数据手册中得到或一致提取出来。由于缺乏更明确的规范,下述各个参数表根据这种爪形曲线(如果可用的话)使用0.5V净空限值,来估算当拉/灌电流为最小值时的“线性”输出电流。具有负载电流时,这一0.5V净空大约处于RRO的边缘(称为部分轨到轨输出),差不多到了非RRO器件的状态。在没有这种曲线或缺乏明确规范行的情况下,另一种方法是取短路电流的1/2。最近, OPA837单位增益稳定放大器数据手册使用了一种新的方式显示可用的“线性”输出电流,如图3所示。最右边的“A”表示经过100%自动测试设备(ATE)筛选,其中条件显示了在±2.5V供电情况下的这类测试设置和限值。

图3:最新的“线性”输出电流规范。

图2所示的爪形曲线非常有用,暗示了2象限输出VI特性。一些较旧型号的高速运算放大器(如OPA690)试图显示更全面的4象限输出VI特性,如图4所示。虽然图中包含很大的信息量(包括爪形曲线部分),却没有引起太大的关注,现在很大程度上已经被TI数据手册抛弃——但它确实出现在较新的Microchip数据手册中(图4~6)。请注意,这个5.5mA静态电流器件可提供更高的输出电流。这是非轨到轨输出设计的主要优点,因为从所需的静态供电电流到可得的输出电流,可获得更高的“功率增益”。

图4:非轨到轨OPA690 4象限输出VI工作范围。

与输出电压摆动范围有两种选择不同,宽带电压反馈运算放大器通常有3种输入范围选择。许多老式的非轨到轨输入(非RRI)器件通常也是非RRO器件(有一些例外)。它们通常要求电源引脚提供1~2V的输入工作电压净空。随着单电源、RRO VFA开始变得流行,对于最早提供的负轨输入(NRI)类型,其输入一般可以摆动到负电源引脚,但通常要求正电源提供1~1.5V的净空。这很快就转移到众多的轨到轨输入(RRI)式CMOS和双极型器件,它们的输入引脚对电源的电压净空降至最小。

随着应用带宽的增加,需要RRI到正电源的应用逐渐减少,高侧电流检测是其中的一个突出应用。对于单电源、直流耦合应用,还有更多的应用只需要输入范围到负电源,而实现从地到某个正电压的输入摆幅。

对于高速互补双极型运算放大器,NRI仅需要一个PNP输入级,与双极型RRI器件相比,这种器件更多一些。在更高速度的应用中,可能“不”需要正轨输入的原因包括:

大多数NRI、RRO型运算放大器采用单电源供电且负电源引脚接地,其线性度不佳,而不能使输出端真正完全摆动到地。大多数PNP输入级可接受真正的地输入而实现单电源工作。现在有很多电路技术都可以实现0V→+Vin输入摆幅,利用直流耦合增益,就可以为I/O引脚提供一些对地净空,从而改善信号通路线性度。OPA830数据手册就使用了其中一种技术,如图5所示。这里采用电源将输入(以及输出)电平转换到略高于地的位置,现在0V到+Vin的输入摆幅工作在输出端,并具有更多的低端净空。这种方法确实需要电源信号吸收该电平转换电流,并且现在该电平转换电源到输出电压具有信号通路。在需要考虑电源抑制比(PSRR)的情况下,如果有参考电压的话,可以使用它实现此电平转换。

图5:直流耦合、单电源、0V输入到电平移位输出的方法

双极型NRI和RRO器件更普遍的问题在输出引脚上。NRI采用的PNP输入通常具有良好的线性度而可以摆动到地,但是对于大部分RRO器件来说,如果硬要它摆动到地的200mV范围以内,则输出会失去线性。使用-0.23V固定负轨发生器LM7705作为负电源,也可以轻松得到200mV的输出净空。在运放应用中使用这样的开关稳压器确实会引起PSRR问题。

稍后将会看到,用FDA对LM7705这种方法进行基准测试,会对这种差分输出高速放大器产生完全的开关噪声抑制。LT6360这种器件包含了内置负电源发生器, 可以实现到地的线性摆动。

现代“互补”双极型(垂直PNP)高速单片VFA最早出现在1989年,由多家供应商推出。经过近30年的产品开发,现有大量的器件可供我们选择。表1到表3列举了少量样本,并给出了一些关键参数。这些参数来自过去10年某个时候对公开数据手册的最佳审查。虽然这些表格出错的可能性很小,但是对设计人员来说,仍然需要仔细审核最新的器件数据表。

从最大工作电源电压(max Vs)可以猜测出该器件的工艺技术。较高的电压通常是双极型的(较慢速的器件中HV CMOS更为常见),而最大Vs较低(<7V)则通常是CMOS或互补SiGe。从输入偏置电流也可判断器件是双极型还是CMOS/JFET。输入偏置电流在μA级别时,可能是双极型的,而如果它在pA级别,则可能是CMOS/JFET。但凡事总有例外,一些器件的输入偏置电流被消除了,显示在nA级别,但实际上是双极型输入。一些较低噪声CMOS器件的输入偏置电流>1nA,输入电容较大。摆动至轨是指净空<0.5V的所有摆动。这些非RRO器件通常是最老的,因为较新的(2008年之后)设计通常都采用RRO。非RRO器件大多数是互补双极型,这由相对较高的最大输入偏置电流能看出来。原始供应商通常会列出来,因为它们与产品型号的前缀相关(例如,LMH表示“线性单片高速”)。

表1:非RRO、单通道、单位增益稳定高速VFA。

RRO VFA器件可以拆分为NRI和RRI器件。为了获得较低的输入噪声,很少有RRO VFA两个输入轨都不包含,如表2所示。为了缩小这个NRI、RRO器件表格,我们用与表1相同的筛选条件,剔除所有RRI器件,只剩下RRO器件。显然,有更多的CMOS器件(Ib<1nA)和更多Vs(最大值)<7V的器件。另请注意,与非RRO器件相比,最大单位增益SSBW下降很大(450MHz对900MHz)轨到轨输出级具有更大的传播延迟,限制了单位增益稳定闭环带宽。

表:2: RRO、单通道、单位增益稳定高速VFA。

最后来看RRIO高速VFA。同样,采用与表2相同的筛选条件,但只包括RRI。这些轨到轨输入级通常在输入端包含一个分频网络或包含一个内部电荷泵,以将输入级偏置在正电源电压以上。

表3: RRIO、单通道、单位增益稳定高速VFA。

为简单起见,很多VFA不同版本没有包含在这些表中,其中有非完全补偿器件、多通道器件,以及已停产的器件。

在本系列的后续文章中我们将对电流反馈放大器(CFA)和全差分放大器(FDA)的I/O电压范围进行讨论。

本文为《电子技术设计》2019年2月刊杂志文章。

(原文刊登于ASPENCORE旗下Planet Analog英文网站,参考链接:Input and Output Voltage Range Issues for High Speed Amplifiers。)

最前沿的电子设计资讯

最前沿的电子设计资讯